| 후난대학, 반도체 칩 3차원 집적공정 개발 | ||

|

||

|

□ 저온의 반데르 발스(VanDer Waals) 기법 사용(5.23)

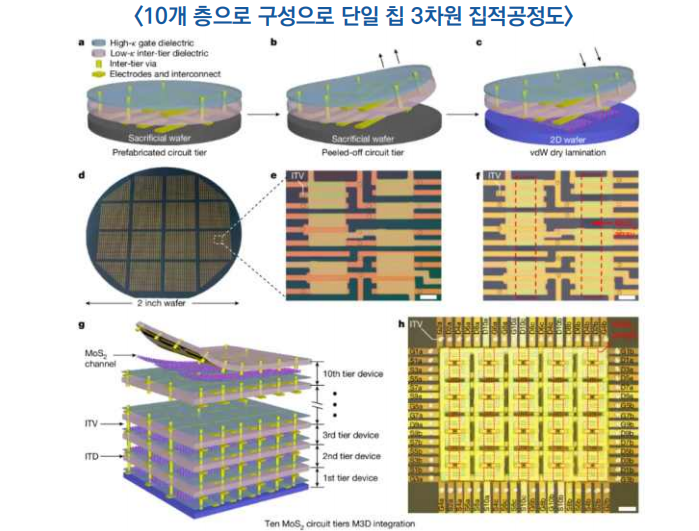

○ 후난대학의 루둥린(陆冬林) 교수 연구진은 반도체의 로직, 저장 및 센싱 등 기능을 수직으로 통합할 수 있는 신형의 단일 칩 3차원 집적공정을 개발

* 3차원 집적이란 여러 개의 독립적인 칩 또는 기능 층을 수직 방향으로 함께 적층하는 장치 시스템

- 연구진은 소스·드레인·게이트 전극, 인레이어 인터커넥트 금속, HKG(high-κ-gate) 유전체, Low-κ 중간층 유전체층, 층간 수직 비아 등 회로의 기능 층을 희생용 웨이퍼에 사전 제작함

- 위 조립식 회로 층을 120°C의 저온에서 반도체 웨이퍼에 집적함으로써 10개 층으로 구성된 반데르 발스(VanDer Waals) 층상조직 형태의 단일 칩 3차원 시스템을 구현함

- 이 공정은 황화몰리브덴 트랜지스터의 전기적 특성에 영향을 미치지 않으며 트랜지스터의 본질적인 성능을 보장할 수 있음

- 이 연구는 단일 칩의 3차원 집적시스템을 위한 저에너지 경로를 제공했다는데 의미가 크고, 관련 논문은 네이처 최근호에 게재

<참고자료>

湖南大学科研团队提出一种新的芯片三维集成工艺

|

- 정책동향

- 이슈리포트

- 통계DB

- 통계DB