| ‘첨단 공정 없이도 이긴다’ – 화웨이의 쿼드칩렛 혁신, NVIDIA를 정조준 | ||

|

||

|

□ 중국 화웨이(華為)가 4개의 반도체를 연결하는 후공정 기술인 쿼드칩렛 특허를 공개했으며, 해당 기술이 미국의 기술 봉쇄를 돌파하고 NVIDIA 추격을 위한 핵심 전략이 될 수 있다고 평가됨(25.6.18)

○ (기술 개요) 화웨이의 쿼드 칩렛(quad-chiplet) 패키징 기술은 하나의 큰 칩을 만드는 대신, 4개의 작은 칩(칩렛)으로 나누어 각각을 연결해 하나의 고성능 AI 가속기로 작동하게 하는 기술임

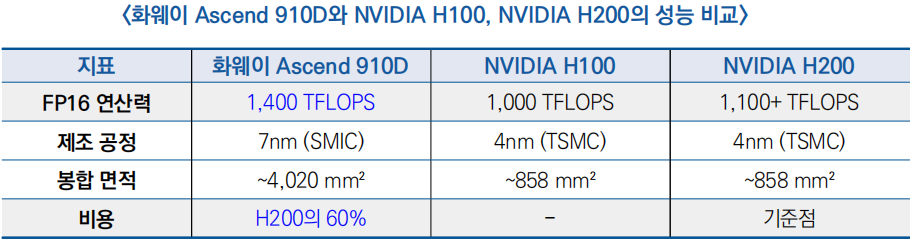

- (브릿지 아키텍처 · 칩렛 통합) 화웨이는 기존의 중개층 방식 대신 분산형 브릿지 아키텍처를 도입해, 4개의 Ascend 910B 칩(각 665㎟)을 하나로 통합한 Ascend 910D 칩(총 면적 4,020㎟)을 구현했음. 이는 극자외선(EUV) 노광 공정 기준으로 마스크 5장 분량에 해당하는 규모이며, 해당 구조는 칩 간 연결 효율을 높여 데이터 전송 병목을 줄이고 전체 연산성능을 향상시키는 데 기여함

- (고대역폭 메모리 · 연산성능 향상) 각 칩에는 4개의 HBM이 연결되어 총 16개의 HBM스택이 통합되며, TSV(실리콘 관통 비아) 기술을 활용해 초고속 연결을 구현했음. 이러한 구조 덕분에 제조 공정이 한 세대 느리더라도, 패키징 기술만으로도 연산성능은 NVIDIA의 H100 수준까지 끌어올릴 수 있는 것으로 평가됨

○ (기술 우위) Tom's Hardware 보도에 따르면 화웨이의 쿼드칩렛은 NVIDIA의 차세대 Rubin Ultra 플랫폼과 유사한 수준에 도달할 수 있으며 공급망 자립화, 비용 경쟁력, 중개층 아키텍처·패키징 혁신 등 기술우위를 보유

- (공급망 자립화) 화웨이는 SMIC의 14nm 공정과 장전과기(长电科技)의 패키징 생산라인을 활용하여, 미국의 첨단 장비 수출 통제를 효과적으로 우회하고 있음

- (비용 경쟁력 · 현지화 생산) 화웨이 Ascend 910D는 NVIDIA H200보다 약 40% 저렴한 생산비용을 달성했음. 이는 국산 공급망 활용, 설계 간소화, 대량 생산을 통해 비용을 효과적으로 절감한 결과임

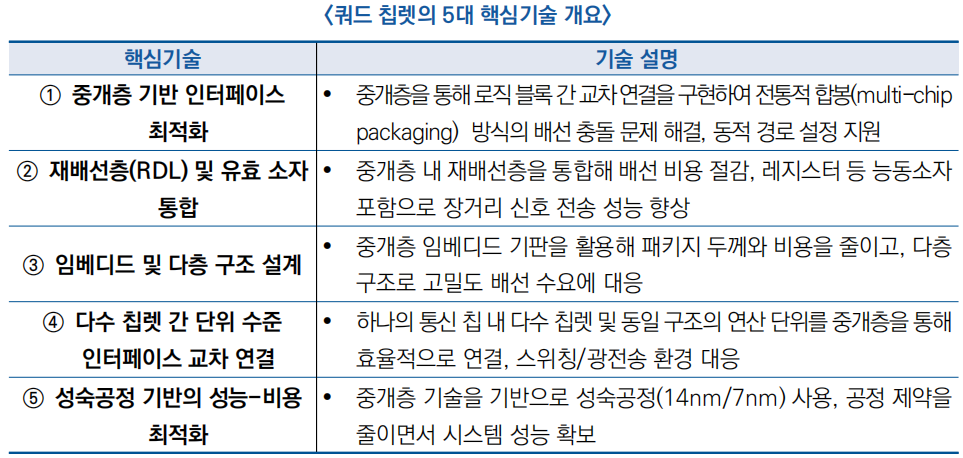

- (중개층 아키텍처 · 패키징 혁신) 화웨이는 실리콘 중개층 기반의 구조를 통해 베어 다이 간 로직 블록과 인터페이스의 교차 연결을 구현함. 이를 통해 회로 충돌 문제를 해소하고, 고대역폭 데이터 전송 및 AI 연산 확장성을 확보

○ (의미) 화웨이의 쿼드칩렛(quad-chiplet) 패키징 기술은 미국의 첨단 반도체 수출제한이라는 불리한 환경 속에서, ‘자국 내 성숙공정(14nm/7nm 등) + 독자적인 첨단 패키징 기술’을 통해 글로벌 반도체 시장에서 새로운 경쟁 구도를 만들어내고 있음

<참고자료>

(25.6.18, 电子工程专辑) 华为“四芯片封装”,能否挑战Nvidia GPU封锁?

작성자: 우만주 연구원(yumanshu87@naver.com)

|

- 정책동향

- 이슈리포트

- 통계DB

- 통계DB